|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

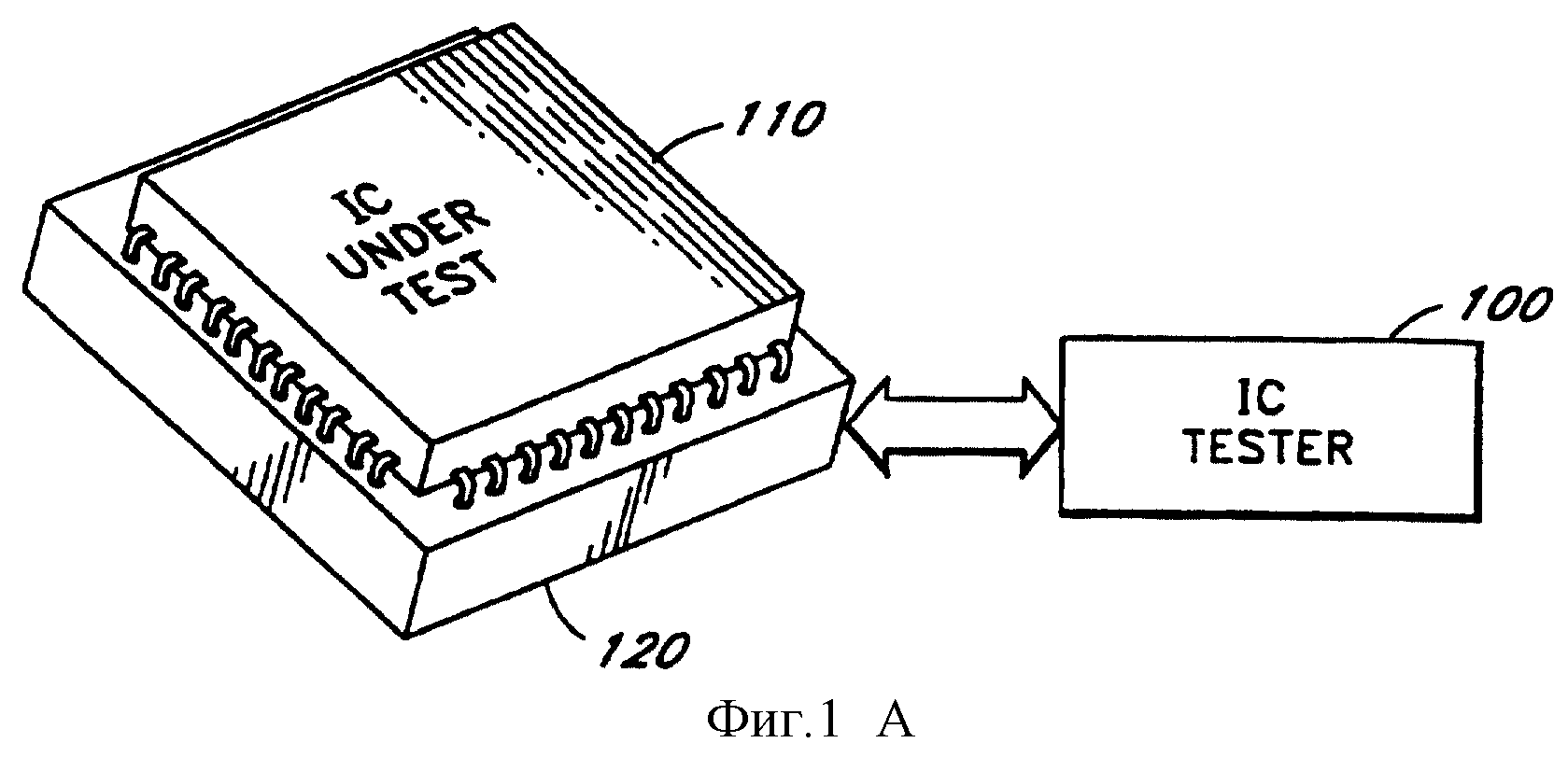

| СПОСОБ И УСТРОЙСТВО БЫСТРОГО И ЭФФЕКТИВНОГО ПЕРЕКЛЮЧЕНИЯ ВЫВОДНЫХ ШТЫРЬКОВ ПРИ ТЕСТИРОВАНИИ ИНТЕГРАЛЬНОЙ СХЕМЫ |  |

Номер публикации патента: 2163023 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | G01R031/28 | | Аналоги изобретения: | US 5066094 A, 08.10.1991. RU 94022611 A1, 10.01.1996. RU 2023641 C1, 09.02.1995. RU 20343069 C1, 30.04.1995. |

| Имя заявителя: | САМСУНГ ЭЛЕКТРОНИКС Ко., Лтд. (KR) | | Изобретатели: | МОУТ Л. Рандалл Юр. (US) | | Патентообладатели: | САМСУНГ ЭЛЕКТРОНИКС Ко., Лтд. (KR) | | Номер конвенционной заявки: | 08/596,043 | | Страна приоритета: | US |

Реферат |  |

Способ переключения выводных штырьков кристалла интегральной схемы ИС для удовлетворения тестовых требований производителя к переключению выводов заключается в том, что параллельно загружают данные из тестера ИС в регистр сдвига периферийного сканирования ИС так, что параллельно загруженные данные являются чередующимися высоко- и низкоуровневыми битами данных. Тестовая комбинация чередующихся битов данных затем фиксируется в регистре фиксации данных и подается на выводные штырьки кристалла ИС. Затем тестовая комбинация сдвигается на один бит в сдвиговом регистре ИС и параллельно загружается в фиксирующий регистр в следующем периоде синхронизации. Таким образом, дополнение тестовой комбинации, подаваемое на выводные штырьки внутренней тестирующей схемой, выдается из кристалла ИС. Затем этот процесс повторяется еще раз для обеспечения чередующегося перехода для каждого из выводных штырьков на кристалле ИС. Техническим результатом является упрощение и повышение надежности тестирования интегральной схемы. 2 с. и 4 з.п. ф-лы, 4 ил.

|